fir滤波器采用了二的补码形式的csd编码算法,能够将常系数编码中的非零位达到最少,从而简化乘法器的结构,提高滤波器的运算速度。

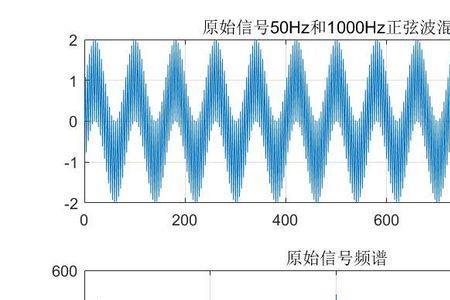

滤波器电路采用veriloghdl设计,最后设计出的基于csd架构的半带fir滤波器在modelsim上通过了功能仿真,并在matlab上进行频谱和时域分析。

结果表明,此设计达到了预期效果,且采用这种方法设计的fir滤波器其性能优于传统方法。

原创 | 2023-01-01 11:37:03 |浏览:1.6万

fir滤波器采用了二的补码形式的csd编码算法,能够将常系数编码中的非零位达到最少,从而简化乘法器的结构,提高滤波器的运算速度。

滤波器电路采用veriloghdl设计,最后设计出的基于csd架构的半带fir滤波器在modelsim上通过了功能仿真,并在matlab上进行频谱和时域分析。

结果表明,此设计达到了预期效果,且采用这种方法设计的fir滤波器其性能优于传统方法。

Copyright 2005-2020 www.kxting.com 版权所有 |  湘ICP备2023022655号

湘ICP备2023022655号

声明: 本站所有内容均只可用于学习参考,信息与图片素材来源于互联网,如内容侵权与违规,请与本站联系,将在三个工作日内处理,联系邮箱:47085,1089@qq.com