高电平输入,输出为低电平低电平输入,输出为高电平。

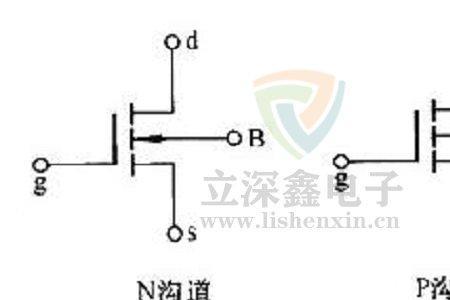

导电沟道的形成

当vGS数值较小,吸引电子的能力不强时,漏——源极之间仍无导电沟道出现。vGS增加时,吸引到P衬底表面层的电子就增多,当vGS达到某一数值时,这些电子在栅极附近的P衬底表面便形成一个N型薄层,且与两个N+区相连通,在漏——源极间形成N型导电沟道,其导电类型与P衬底相反,故又称为反型层。vGS越大,作用于半导体表面的电场就越强,吸引到P衬底表面的电子就越多,导电沟道越厚,沟道电阻越小。

原创 | 2022-12-06 18:43:54 |浏览:1.6万

高电平输入,输出为低电平低电平输入,输出为高电平。

导电沟道的形成

当vGS数值较小,吸引电子的能力不强时,漏——源极之间仍无导电沟道出现。vGS增加时,吸引到P衬底表面层的电子就增多,当vGS达到某一数值时,这些电子在栅极附近的P衬底表面便形成一个N型薄层,且与两个N+区相连通,在漏——源极间形成N型导电沟道,其导电类型与P衬底相反,故又称为反型层。vGS越大,作用于半导体表面的电场就越强,吸引到P衬底表面的电子就越多,导电沟道越厚,沟道电阻越小。

Copyright 2005-2020 www.kxting.com 版权所有 |  湘ICP备2023022655号

湘ICP备2023022655号

声明: 本站所有内容均只可用于学习参考,信息与图片素材来源于互联网,如内容侵权与违规,请与本站联系,将在三个工作日内处理,联系邮箱:47085,1089@qq.com