计数器实际上是对时钟脉冲进行计数,每来一个脉冲,计数器状态改变一次。

8421BCD码十进制加计数器在每个时钟脉冲作用下,触发器输出编码值加1,编码顺序与8421BCD码一样,每个时钟脉冲完成一个计数周期。由于电路的状态数、状态转换关系及状态编码都是明确的,因此设计过程较简单。

d触发器构成计数器的原理

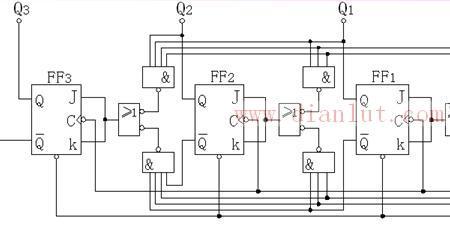

原理异步二进制计数器是计数器中最基本最简单的电路,它一般由接成计数型的触发器连接而成,计数脉冲加到最低位触发器的CP端,低位触发器的输出Q作为相邻高位触发器的时钟脉冲。

原创 | 2022-11-18 18:47:13 |浏览:1.6万

计数器实际上是对时钟脉冲进行计数,每来一个脉冲,计数器状态改变一次。

8421BCD码十进制加计数器在每个时钟脉冲作用下,触发器输出编码值加1,编码顺序与8421BCD码一样,每个时钟脉冲完成一个计数周期。由于电路的状态数、状态转换关系及状态编码都是明确的,因此设计过程较简单。

d触发器构成计数器的原理

原理异步二进制计数器是计数器中最基本最简单的电路,它一般由接成计数型的触发器连接而成,计数脉冲加到最低位触发器的CP端,低位触发器的输出Q作为相邻高位触发器的时钟脉冲。

Copyright 2005-2020 www.kxting.com 版权所有 |  湘ICP备2023022655号

湘ICP备2023022655号

声明: 本站所有内容均只可用于学习参考,信息与图片素材来源于互联网,如内容侵权与违规,请与本站联系,将在三个工作日内处理,联系邮箱:47085,1089@qq.com